Lekcja 1- podstawowe funktory logiczne

1.Algebra Boole'a - podstawowe informacje

ALGEBRA BOOLE'A

algebra ogólna stosowana w matematyce, informatyce teoretycznej oraz elektronice cyfrowej. Jej nazwa pochodzi od nazwiska matematyka, filozofa i logika George'a Boole'a. Teoria algebr Boole'a jest działem matematyki na pograniczu teorii częściowego porządku, algebry, logiki matematycznej i topologii.

Algebra Boole'a to struktura algebraiczna  , w której

, w której  i

i  są działaniami dwuargumentowymi,

są działaniami dwuargumentowymi,  jest operacją jednoargumentową, a 0 i 1 są wyróżnionymi różnymi elementami zbioru

jest operacją jednoargumentową, a 0 i 1 są wyróżnionymi różnymi elementami zbioru  , spełniająca następujące warunki dla wszystkich

, spełniająca następujące warunki dla wszystkich  :

:

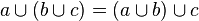

-

łączność

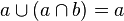

przemienność

absorpcja

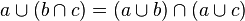

rozdzielność

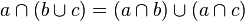

pochłanianie

2. Podstawowe funktory logiczne

| SUMA LOGICZNA ( OR )

y = a + b

|

ILOCZYN LOGICZNY ( AND )

y = a * b

|

NEGACJA ( NOT )

_

|

NIE SUMA LOGICZNA ( NOR )

![]()

|

a |

b |

y |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

![]()

NIE ILOCZYN LOGICZNY ( NAND )

![]()

|

a |

b |

y |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

![]()

3.Zasada działania bramki NAND

Objaśnienie zasady działania bramki NAND na podstawie struktury wewnętrznej wykonanej w technologii TTL.

Tranzystor wieloemiterowy T1 realizuje operację AND. Tranzystor T2 z rezystorami R2 i R3 pracuje w konfiguracji wzmacniacza symetryzującego (odwracacz fazy ) wytwarzającego odpowiednie poziomy napięć na bazach tranzystorów T3 i T4. Tranzystory te tworzą stopień wyjściowy o małej impedancji zarówno dla stanu o na wyjściu ( stan włączenia bramki), jak i 1 (stanu wyłączenia). Dioda D1 służy do zapewnienia odpowiednich warunków pracy stopnia wyjściowego, tj. skutecznego zatykania tranzystora T3 gdy tranzystorT4 jest nasycany. Jeżeli na wszystkich emiterach tranzystora T1, czyli wejściach bramki, jest stan wysoki, to złącza emiter-baza tego tranzystora są spolaryzowane zaporowo ( typowo wartość prądu wpływającego do jednego emitera wynosi 40 A), natomiast złącze baza-kolektor przewodzi. Tranzystor jest więc spolaryzowany inwersyjnie, tranzystory T2 i T4 są w stanie nasycenia, T3 jest zatkany. W tym stanie włączenia typowa wartość napięcia wyjściowego Uol wynosi 0,2 V, przy maksymalnym prądzie obciążenia wpływającym do bramki równym 16 mA. Gdy chociaż na jednym z emiterów tranzystora T1, a więc na jednym z wejść bramki, jest stan niski (typowo UIL = 0,2V) wówczas tranzystor ten jest nasycony i maksymalna wartość prądu wypływającego z jego emitera wynosi 1,6 mA. W punkcie A wystąpi potencjał o wartości 0,1 do 0,2 wolta. W tym stanie tranzystory T2 i T4 są w stanie zatkania, tranzystor T3 pracuje w zakresie liniowym jako wtórnik emiterowy. Typowa wartość napięcia wyjściowego UOH wynosi wówczas 3,5 V, przy maksymalnym wypływającym prądzie obciążenia z wyjścia bramki równym 0,4 mA. Stosunek maksymalnych wartości prądów wyjściowych do wejściowych w stanie włączenia i wyłączenia wynosi 10. Obciążalność wyjściowa standardowej bramki TTL wynosi N = 10, co oznacza , że do wyjścia bramki może być przyłączonych 10 wejść innych bramek.

4.

Bramki AND-OR-INVERT

.Funkcję AND-OR-INVERT (inaczej AND-NOR) realizują układy NAND-OC. Funkcje tego typu występują nie tylko w przypadku "sumowania na drucie". Można je często spotkać w: układach arytmetycznych, licznikach, rejestrach, różnego rodzaju multiplekserach itp. Z tego powodu została ona potraktowana jako typowy blok produkowany jako element scalony. Schemat ideowy bramki AND-OR-INVERT (450) pokazano na rys. 6.12. Na schemacie zaznaczono dodatkowe wejścia dla ekspandera (460) rozszerzającego liczbę wejść bramki. Schemat ideowy czterowejściowego ekspandera przedstawiono na rys. 6.13. Liczba ekspanderów, jaką można dołączyć do elementu podstawowego, jest ograniczona. Element bez ekspandera ma taki sam czas propagacji jak element NAND. Każdy dołączony ekspander zwiększa ten czas o kilka nanosekund. Na rys. 6.14 przedstawiono układ, w którym liczbę bloków AND poszerzono do czterech.

Rys. 6.12. Schemat bramki AND-OR-INVERT 450

Rys. 6.13. (z lewej) Schemat ideowy ekspandera 460.

Rys. 6.14. (z prawej) Bramka AND-OR-INVERT z dwoma ekspanderami

Bramki logiczne

Najprościej mówiąc bramka logiczna jest urządzeniem, które przetwarza bity wejściowe dając w wyniku bit wynikowy, którego wartość jest pewną funkcją logiczną wartości bitów wejściowych. W technice cyfrowej bity przedstawiane są najczęściej poziomem napięcia. Jeśli poziom ten zawiera się w zakresie od 0,4...0,8V, to mamy do czynienia ze stanem niskim L lub 0. Poziom od 2,0...2,4..5V oznaczamy jako H lub 1. Są to tzw. poziomy logiczne. Napięcia takie doprowadza się do wejść bramek. Na wyjściu bramki otrzymuje się napięcie 0,4V (L - 0) lub 2,4V (H - 1), które jest funkcją logiczną doprowadzonych do jej wejść poziomów logicznych. W logice obowiązują tylko dwie wartości - 0 (tzw. fałsz - ang. false) oraz 1 (tzw. prawda - ang. true). Wartości te mogą być bezpośrednio przedstawiane przy pomocy bitów.

Do konstrukcji nawet najbardziej złożonych układów cyfrowych (np. mikroprocesor) konieczne są trzy podstawowe elementy logiczne: NOT, AND oraz OR i jeden element pamięciowy, zwany przerzutnikiem. Przy omawianiu bramek będziemy stosować oznaczenia 0 dla poziomu L (0,4V) oraz 1 dla poziomu H (2,4V). O ile nie będziesz konstruował układów cyfrowych, wartość tych napięć nie jest dla ciebie specjalnie istotna.